- Installing modelsim altera vhdl model files full#

- Installing modelsim altera vhdl model files software#

- Installing modelsim altera vhdl model files code#

- Installing modelsim altera vhdl model files free#

Installing modelsim altera vhdl model files code#

Now, let’s run and debug the source in the VS Code editor.I use Visual Studio Code more and more and today that is my favorite editor.If I want to use tree-sitter-verilog, can my extension only run in a specific version of Visual Studio Code cause of the nodejs version? The text was updated successfully, but these errors were encountered:.They share a library that implements the client and server part of the protocol. There was a problem preparing your codespace, please try again. by the C99 standard, but not supported by MS Visual Studio. Code Runner offers several ways to run code from the editor.Standardized design libraries are typically used and are included prior to the entity declaration. A bit value of one would be expressed as 1'b1. You didn't declare a in the list, and you use a in the code.

Installing modelsim altera vhdl model files full#

Combined with the Jupyter extension, it offers a full environment for Jupyter development that can be enhanced with additional language extensions. Perhaps you are compiling with a Verilog Testbench Runner. When you successfully compile a VHDL code, it is more likely that your VHDL code is working compared to Verilog. Use CMake to target multiple platforms from the comfort of a single IDE. You could also express this same value in a hexadecimal Implement a 5-to-32 Line Decoder in Verilog using VisualStudio Code using starter. Navigate back to Visual Studio Code and search for ESLint in the Extensions tab. Reserve a code to reset state of operation This is o.Reserve a two codes for run / stop control.Write and run R code in Visual Studio Code The vscode-R extension instructions suggests that users open a folder when working in R, not just create a new file.my problem is why the I value incremented at valid not equal to one This weekend I went from File-New-Project, Right-Click - Build to a ULX3S bit file! This was originally supposed to be my blog on using Visual Studio to build (synthesize) Verilog FPGA code.

Installing modelsim altera vhdl model files free#

Code Editing Notebooks in Visual Studio Code VS Code is a free code editor and development platform that you can use locally or connected to remote compute. Icarus is maintained by Stephen Williams and it is released under the GNU GPL license. We noted above that the vco script decides to set the mode to "32", despite running on the 64-bit machine.How to run verilog in visual studio code Find and select Run Code Configuration. Why is it running the vish program? In any case, this error makes a little bit of sense. vish: error while loading shared libraries: libX11.so.6: cannot open shared object file: No such file or directory If we try to run, for example, the vsim program we get: "if [ catch /modelsim_ase/linuxaloem directory, we find a bunch of actual executables (i.e.

Installing modelsim altera vhdl model files software#

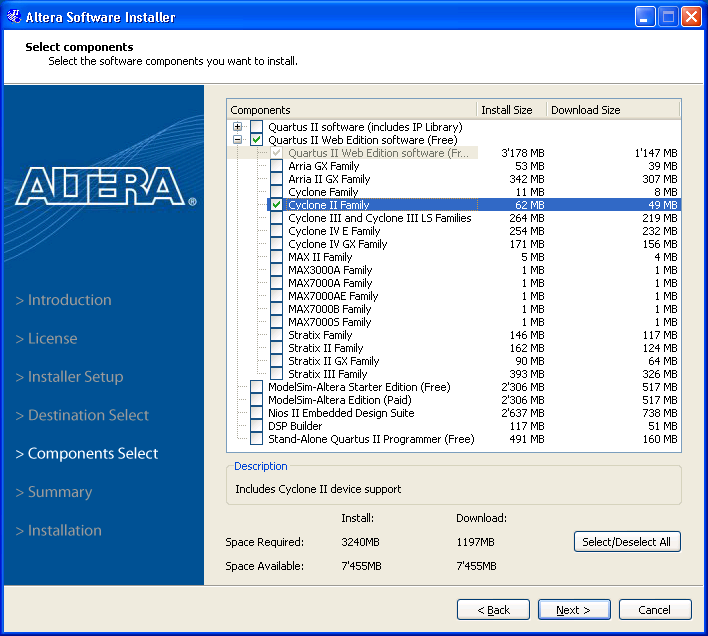

Nativelink TCL script failed with errorInfo: Can't launch ModelSim-Altera Simulation software - make sure the software is properly installed and the environment variable LM_LICENSE_FILE or MGLS_LICENSE_FILE points to the correct license file. Nativelink TCL script failed with errorCode: issued_nl_message =The following additional information is provided to help identify the cause of error while running nativelink scripts=

Sourced NativeLink script /opt/Altera/intelFPGA_lite/17.0/quartus/common/tcl/internal/nativelink/modelsim.tclĮrror: Can't launch ModelSim-Altera Simulation software - make sure the software is properly installed and the environment variable LM_LICENSE_FILE or MGLS_LICENSE_FILE points to the correct license file.Įrror: NativeLink simulation flow was NOT successful Info: Starting NativeLink simulation with ModelSim-Altera software Quartus sim root : /opt/Altera/intelFPGA_lite/17.0/quartus/eda/sim_lib

Quartus root : /opt/Altera/intelFPGA_lite/17.0/quartus/linu圆4/ Info: NativeLink has detected Verilog design - Verilog simulation models will be used Info: Start Nativelink Simulation process IOW, you can't keep the dialog box open to help find the file, you have to make note of where the file is, close the dialog box, then open the file. Meaning you have to make the dialog box go away before you can open the file it tells you to check for more information. where the error message says to check for more details) are only populated after you hit OK.

0 kommentar(er)

0 kommentar(er)